Hardware-Based Speculation

Motivation

With branch prediction, instructions after branches get fetched early into processor

- So far, branch prediction lets us fetch insturctions after a branch, but we cannot execute them

If we execute instructions after a branch, what happens if the prediction is incorrect?

- Branch Prediction: saving cycles because you can fetch before knowing the outcome

- Speculation (speculative execution): Saving cycles because you can execute before knowing branch outcome

Storing Speculative Values#

- For this to work, you need a place to store speculative values

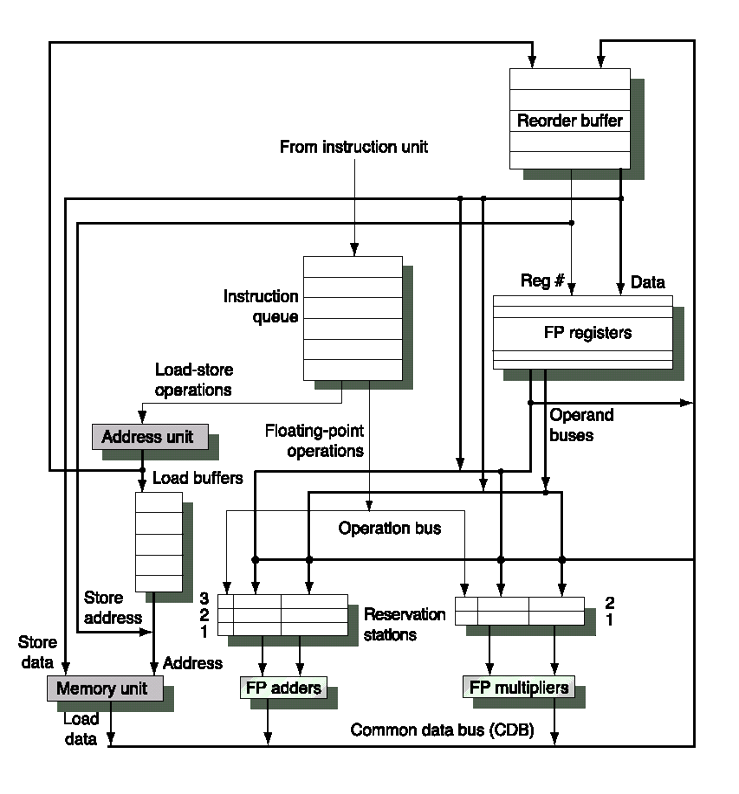

- Reorder Buffer

- In order (like a queue)

- Four fields

- Instruction type

- Destination Register

- Value field

- Read field (is instruction complete?)

Four Stages with Speculation#

- Issue: Send an instruction to a reservation station

- Execute: If operands are ready, then execute

- Write Result: Write to common data bus and the result is stored in the reorder buffer

- Commit: Write result from the reorder buffer into the register file

- On a branch mispredict, clear out instructions after a branch